NXP Semiconductors MCX N23x Highly Integrated MCUs

NXP Semiconductors MCX N23x Highly Integrated MCUs operate with a high-performance Arm® Cortex®-M33 running up to 150MHz, 1MB of Flash, 352KB ECC RAM, and SmartDMA. The MCX N23x is optimized for cost, memory, and system performance and provides a single-core option with efficient workload distribution to the analog and digital peripherals. NXP supports the MCXN236 device with tools and software, including hardware evaluation boards, software development IDE, example applications, and drivers.

The EdgeLock® Secure Enclave featured on the MCX N23x is a self-contained, on-die hardware security subsystem with an independent dedicated security core, internal ROM, and secure RAM. The MCUs support state-of-the-art side-channel attack-resilient symmetric and asymmetric crypto accelerators and hashing functions for security services.

The NXP MCX N23x MCUs support the MCUXpresso Developer Experience to ease, optimize, and help accelerate embedded system development.

Features

- Arm Cortex-M33 150MHz with 618CoreMark® (4.12CoreMark/MHz)

- Up to 1MB Flash, 352KB SRAM

- Platform security with EdgeLock secure enclave, core profile

- -40°C to +125°C temperature range

- Down to 50μA/MHz active current, 3.0μA power-down mode with RTC enabled and 352KB SRAM retention, 1.5μA deep power-down mode with RTC active and 32KB SRAM

Applications

- Industrial

- Energy storage and management system

- Smart metering

- Factory automation

- Industrial HMI

- Mobile robotics ecosystem

- Motion control and robotics

- Motor drives

- Brushless DC Motor (BLDC) Control

- Permanent Magnet Synchronous Motor (PMSM)

- Edge AI/ML anomaly detection and predictive maintenance

- Smart home

- Home control panel

- Home security and surveillance

- Major home appliances

- Robotic appliance

- Smart speaker

- Soundbar

- Gaming accessories

- Smart lighting

- Smart power socket and light switch

Specifications

- Security

- TrustZone for Armv8M

- Secure boot, firmware update, and debug authentication using ROM

- EdgeLock secure subsystem (ELS) S50

- Public-key cryptography (PKC)

- Internal flash memory interface with on-the-fly PRINCE decryption and encryption

- Physically Unclonable Function (PUF) hardware options

- Factory Root of Trust (RoT) programming

- Tamper detection

- Analog and digital glitch detection

- Code Watchdog (CDOG)

- Intrusion and Tamper Response Controller (ITRC)

- Industrial strength

- Industrial temperature rating

- Industrial communication protocol support (CAN-FD)

- High-resolution mixed-signal analog

- BLDC and PMSM motor control support

- Integrated sensor interfaces of I3C, I2C, SPI, and UART

- 15-year longevity

- Configurable RAM ECC

- Power-efficient operating modes

- 50μA/MHz (3.3V at 25°C) in Active mode (core clock 150MHz, while executing from flash, DC/DC enabled)

- 124μA in Deep Sleep mode (full 352KB RAM retention, 3.3V at 25°C)

- 2.39μA in Power Down mode (full 352KB RAM retention, 3.3V at 25°C)

- 1.5μA in Deep Power Down mode, 5.6ms wake-up (RTC enabled and 32KB RAM and Reset pin enabled, 3.3V at 25°C)

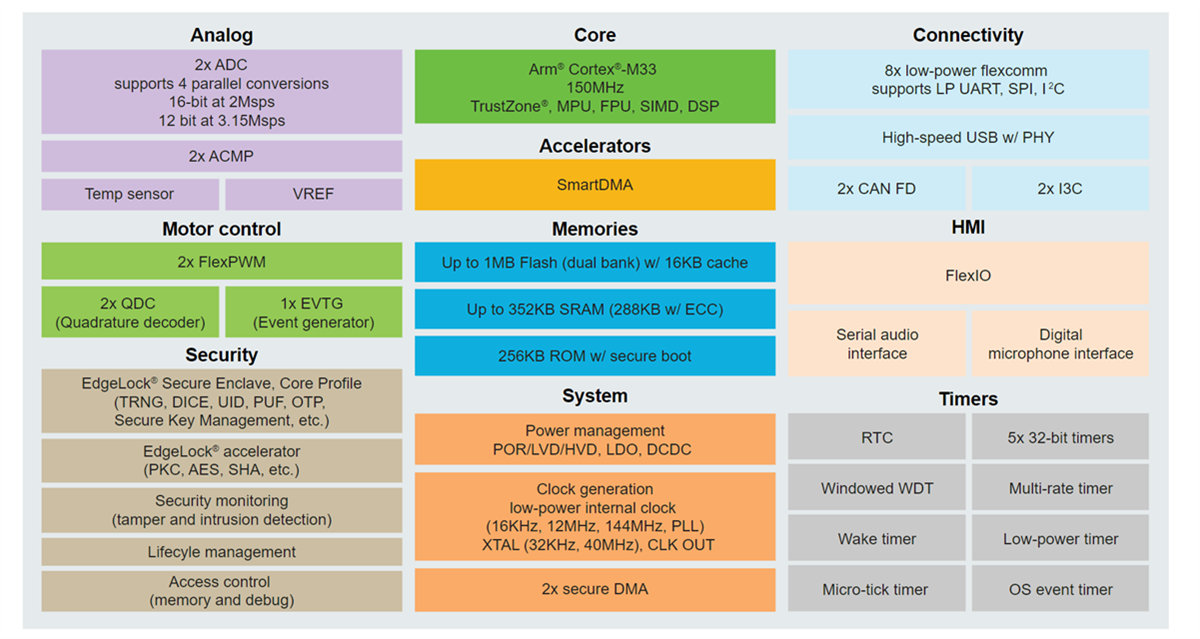

Block Diagram

Architecture